# Processor HC680 fictive

# documentation of simulation

pictures Windows variant

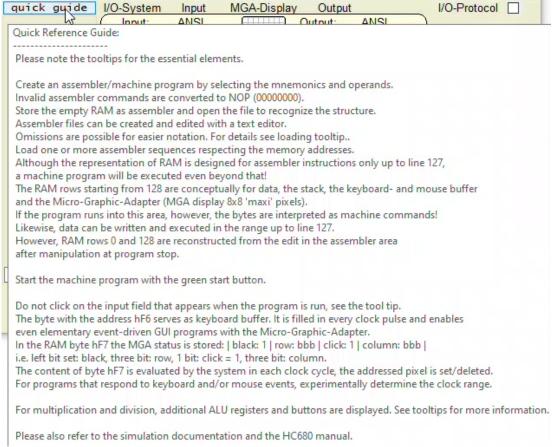

The simulation includes the structure and functionality of the processor and important assemblies of the system. Thereby both the execution of the machine program and its creation by the assembler are realized in a simulation window. Assembler programs can be stored and loaded.

#### data of the system

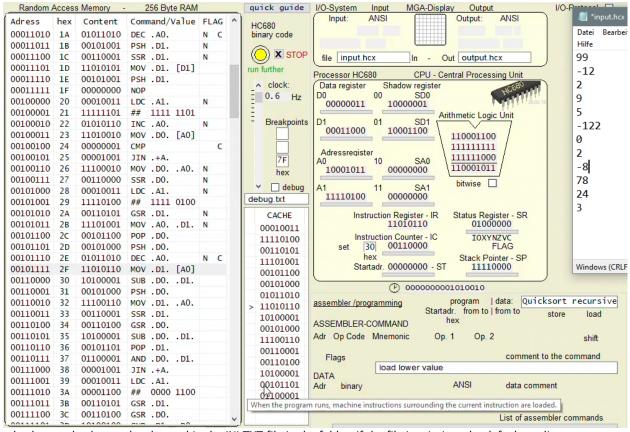

processor: HC 680 fictive

processing width: 8 bit data and addresses

command length: 1 byte address range: 256 byte

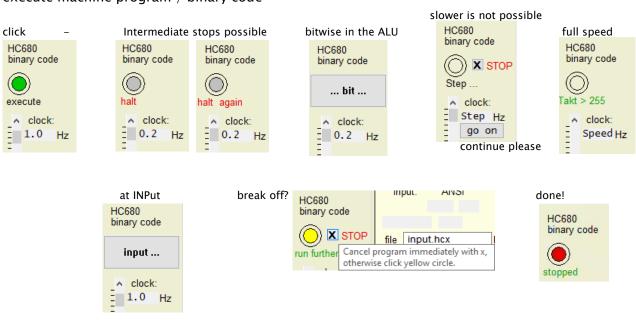

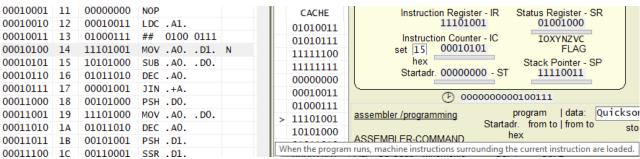

clock pulse: Clock: single step, 0.1Hz to 255Hz, unbraked

registers: 4 general registers with shadow register, start address (ST)

instruction register (IR), instruction counter (IC), status register (SR),

stack pointer (SP)

flags: Negative (N), Zero (Z), oVerflow (V), Carry (C) and I/O Bits

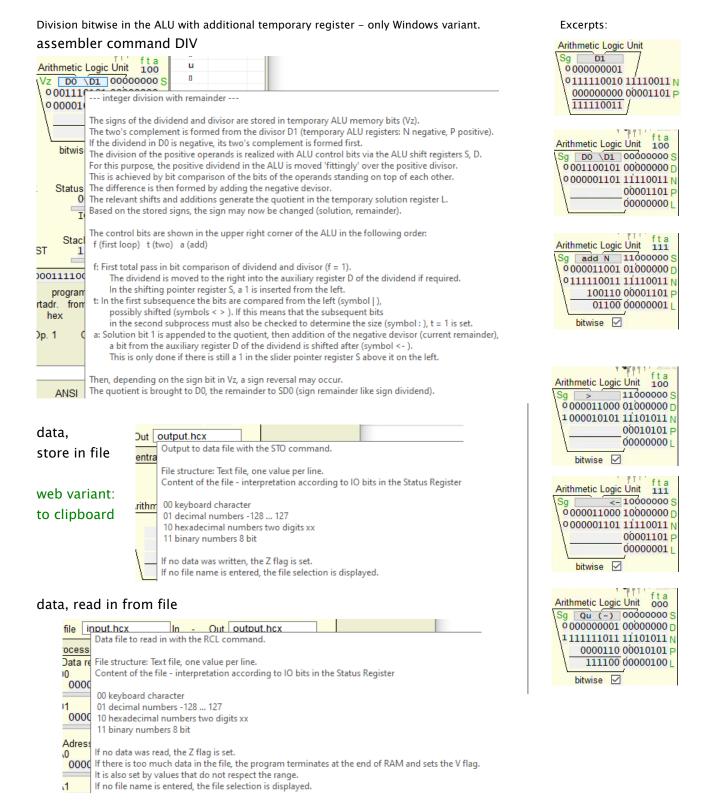

arithmetic unit: Arithmetic Logic Unit (ALU), 8+1 bit sign extension for addition,

multiplication by Booth, division with remainder, ALU bitwise representable

numberspace: decimal from -128 to 127

graphic: 8x8 maxi pixel display, 8 byte shared memory

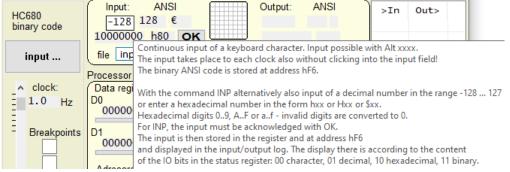

in and output: by I/O bits: keyboard characters, decimal, hexadecimal, - output also binary

files: by I/O bits: keyboard characters, decimal, hexadecimal, binary

breakpoints: 3 - changeable during program execution

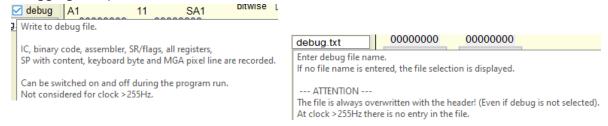

debug: any section, into selectable file

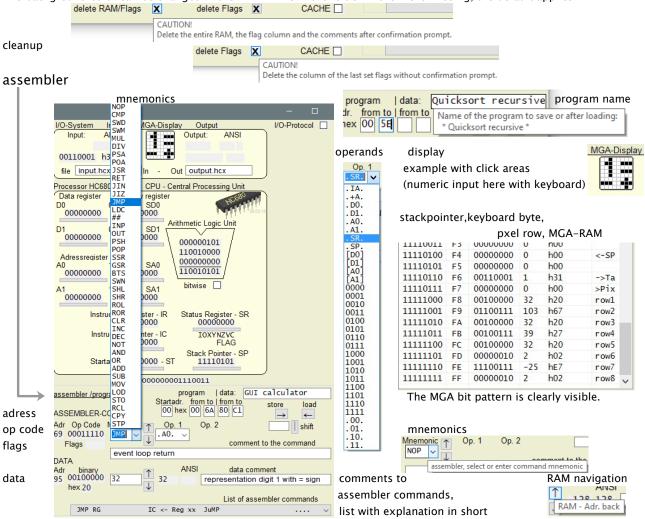

assembler: 40 mnemonics, 57 commands by addressing modes – see manual

\_\_\_

The user assistance is realized via extensive, tooltips (can be switched off in Windows variant).

The background color can be changed in the INI.TXT file in the folder. If the file is missing, the default applies.

comment to the command command comments Enter a comment to the command - even longer than input field, will be visible in the tooltip. data comment Enter a comment to the constant - even longer than input field, will be visible in the tooltip. The complete list of assembler commands with explanation in short form. - Meaning Command/Addressing No OPeration

No OPeration

CoMPare D0, D1

SWap D0, D1

SWap D0, D1

SWap Memory Adr(D0), Adr(D1)

MULtiplication D0 <- D0\*D1

DIVision D0 <- D0\D1 Rest SD0

PuSh All Stack <- A,D, SR Reg.

POp All SR,D,A reg. <- Stack

Jump SubR. S<-IC+1,IC<-IC+A1/IC<-A0+A1+ST

N=1: IC <- IC + A1 Jump If Negative

Z=1: IC <- IC + A1 Jump If Zero

IC <- IC + A1 Jump

RETturn subroutine IC <- Stack

LoaD Constant reg xx <- next Byte ##

C ## Constant Byte

N=1: IC <- A0 +A1 +ST Jump If Negative

Z=1: IC <- A0 +A1 +ST Jump If Zero

IC <- A0 +A1 +ST Jump If Negative

Z=1: IC <- A0 +A1 +ST Jump If Negative

Z=1: IC <- Reg xx Jump If Negative

Z=1: IC <- Reg xx Jump If Negative

Z=1: IC <- Reg xx Jump If Zero

IC <- Reg xx Jump If Zero I/O-Protocol ☑ No OPeration NZVC CMP >In SWD SWM input - output € MUL NZVC protocol DIV PSA POA NZVC -128 -128 NZVC h80 JSR JIN JIZ . . . . h80 >1000 0000. .... .1000 0000> NZ.. . . . . In- and Output protocol . . . . commands INP and OUT - display of values . . . . NZ.. INPut interpretation according to IO bits in the Status Register reg xx OUTput OUTput <- reg xx PuSH Stack <- reg xx POP reg xx <- Stack Set Shadow Register reg NZ.. 00 keyboard character Set Shadow Register reg xx -> Sxx

Get Shadow Register reg xx <- Sxx

BitTest reg xx with Shadow register

SWap Nibble reg xx

SHift Left reg xx

SHift Right reg xx

ROtate Left 01 decimal numbers -128 ... 127 NZ.. 10 hexadecimal numbers two digits xx NZ.. 11 binary numbers 8 bit (over both columns!) NZ. >Input. NZ.C .Z.C NZ.C .Output> ROtate Left ROtate Right CLear Register INCrement rea xx NZ.C .Z.. NZVC reg xx reg xx INCrement reg

DECrement reg

Reg xx <- NOT reg

Reg yx <- reg yy

Reg yy <- reg yy

MOVe Adr(reg yy)

MOVe reg yy

MOVe reg yy ... visibility rea xx reg xx NOT reg xx reg yy AND reg yy OR NZVC NZ.. NZ.. I/O-Protocol (bitwise) reg xx reg xx reg xx >In Out> Visibility of the input and output protocol. NZ. NZVC NZVC Adr(reg xx) ... clear protocol reg xx Adr(reg xx) NZVC Delete input and output protocol without asking. I/O-Prot. delete reg xx NZ.. reg xx

Adr(reg xx)

reg xx

SR

SP NZ.. MOVe <-NZ.. reg vv The 9-bit ALU at work. NZ.. reg yy SR SP MOVe MOVe MOVe reg xx View the individual bits at clock speed. <- reg xx <- CC.. (2bit I0) <- Adr(A0+A1+ST) NZ.. MOVe SR Arithmetic Logic Unit MOVe reg xx MOVe Adr(AO+A1+ST) <- reg xx <- Adr(h80+A1+ST) NZ.. MOVE AGR(AUFAIFSI) <- reg xx

LOad Data reg xx <- Adr(h80+A1+ST)

STOre file <- Adr(h80+A1+ST) D0 byte /D1

ReCalL Adr(h80+A1+ST)<- file /D1 read D0

CoPY Adr(A1)<-Adr(A0) D0 byte via D1

StoP P. stop, flags from pre-command NZ.. 111110100 STO RCL (IO) 1111111101 CPY .7V. 111000 10001 Meaning Command/Addressing Mnem OP OP bitwise Display the calculation process in the ALU bitwise. assembler command MUL Status Reg During the bitwise representation in the ALU: 0100 \* no running keyboard input Arithmetic Logic Unit no mouse handling no stopping possible with start button 000000000 00000100 4 Stack P 1111111100 111111100 S Booth multiplication 000000 11100 10000001 0 (bitwise in the ALU with additional temporary registers) bitwise 🗸 4» Booth --- multiplication according to Booth ---Register D0 is temporarily stored in temporary ALU register A (for addition). Status Register The two's complement -D0 is formed and stored in the temporary register S. 00000001 The 16-bit result is calculated step by step in the bottom line. For this purpose, IOXYNZVC the left byte is initialized with 0 and D1 is stored on the right and the auxiliary bit x is set to 0 next to it. FLAG Stack Pointer Sequence control takes place after the last two bits of the result line (with auxiliary bit x): 11110101 >> The result line is shifted 1 bit to the right, the auxiliary bit is dropped out, 0010000100 on the left, the bit identical to the bit shifted away is added as a sign extension. program | data: only >> from to | from add >> D0 is added, then >> hex sub >> -D0 is added, then >> Op. 2 Op. 1 The left byte of the last line is copied to the top line as a subtotal. (with sign expansion) After 8 steps, the 16bit result (without auxiliary bit x) is obtained in the lower double register. The right byte (low byte) is brought to D0.

Then check for displayability in the range -128 ... 127 and set the flags.

input (continuously a keyboard character or with command INP)

### debugging- only Windows variant

### example in assembler "sum exceeded until 50" - stored as a text file

```

HC680 assembler

; sum exceeded until 50

; Startadr.

00: ST

; - comment

Adr Mnm

_0p_ _0p_

00: MOV .SR. .01.

;output decimal

01: LOD .D1.

;load target sum from h80

02: INC .A1.

;incrementing the address index register A1 to load the next constant

03: LOD

;load jump difference for IC relative jump in A1

.A1.

04: PSH .D0.

;put initial value \emptyset on the stack for cumulating

05: INP .A0.

;-INPUT- data into address register - is possible!

;get cumulated sum from stack

06: POP .D0.

.A0.

;sum with input value

07: ADD .D0.

08: PSH .D0.

;put sum back on stack

09: CMP

;compare sum with target sum (D0-D1 without result)

0A: JIN

.+A.

;IC-relative jump to input, if target sum is not yet reached

0B: OUT .D0.

;-OUTPUT-

OC: STP

;done!

;sum up to 50

80: 50

h32

;IC-relative destination address (five commands back)

81: -5

hFB

```

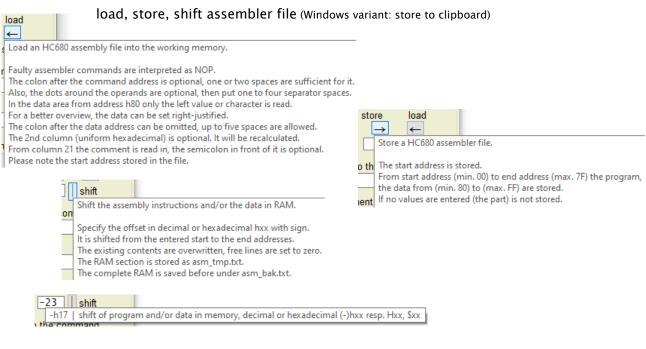

When creating with a text editor, the colon, the dots before and after the operands and the semicolon can be omitted.

After Mnm and between the operands up to 4 spaces are allowed, before Mnm two.

Before the data up to five blanks are allowed for separation, thus right-justified notation is possible.

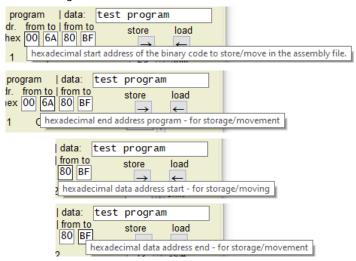

#### address ranges of the assembler file

## execute machine program / binary code